## QuickLogic's eFPGA Technology Delivers Post Manufacturing Flexibility

QuickLogic's Australis™ IP Generator enables quick delivery of a customized eFPGA IP core tailored to your requirement.

The Australis IP Generator flow uses a standard cell ASIC flow to automate the creation of the eFPGA IP. It enables delivery of customized eFPGA IP for a multitude of use cases, such as addressing changing market conditions, supporting new standards, offloading AI/ML workloads, and creating product variants.

| I/F | I/F | I/F  | )/F  | i/F | I/F | i/F | )/E |

|-----|-----|------|------|-----|-----|-----|-----|

| 1/F | СLВ | CLB  | BRAM | DSP | CLB | СГВ | 1/F |

| I/F | CLB | ĊLB  |      |     | CLB | CLB | I/F |

| I/E | CLB | CLB  |      | DSP | CLB | CLB | I/F |

| I/E | CLB | ССЕВ | BRAM |     | CLB | CLB | Ñέ  |

| I/E | CLB | CLB  |      | DSP | СLВ | CLB | I/F |

| )/F | СЦВ | CLB  |      |     | CLB | CLB | I/E |

| 1/1 | ı/r | 1/F  | 1/1  | VE. | 1/1 | W   | 1/0 |

eFPGA Architecture

#### Australis IP Generator: Delivers customized eFPGA IP blocks in weeks, not months.

**Customization –** eFPGA IP can be generated/customized to any foundry/process technology within days for a process we already support and within a quarter for new process technologies.

**Fast time-to-market** – Australis does not use fixed arrays, so you have complete freedom to design your core the way you want.

Flexibility to meet your SoC design requirements – With Australis, you can specify the number of DSP, LUT, and BRAM columns, as well as the specific placement of these columns. You can also define the size of the X/Y array.

**Cost Effective –** Our automated approach to core customization significantly reduces costs and time.

### **Foundry Partners**

Learn more about Australis

# QuickLogic's eFPGA Technology Delivers Post Manufacturing Flexibility

#### Aurora™ FPGA User Tools

Scalability • Longevity • Full Code Transparency

### Aurora Empowers eFPGA Designers with Greater Transparency and Control

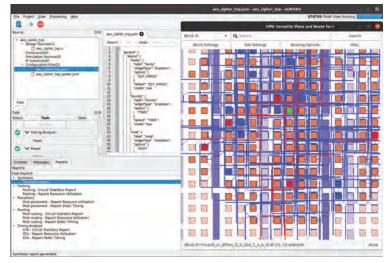

Aurora 2.1 is a fully open-source development tool suite for eFPGA designers. It supports all major HDLs, including Verilog, System Verilog, and VHDL. It is based on open-source synthesis (Yosys), Versatile Place and Route (VPR), and bitstream generation (OpenFPGA) software. The fully integrated suite of tools enables eFPGA designers to go from RTL-to-bitstream for QuickLogic's eFPGA IP.

**Aurora User Tools**

**Simplified Evaluation –** Supports quick and easy evaluation of eFPGA technology for SoC applications.

**Architectural Trade-Offs** – Let's you fine-tune the amount of logic (LUTs), BRAM, and DSP blocks in your eFPGA IP to meet your specific requirements.

**Inspectability –** Open-source based Aurora promotes transparency; the code is easily inspectable and can be continuously improved by the development community.

**Future-Proof** – Aurora is built using readily available open-source components that the broader community is actively improving upon, ensuring that users have access to the latest tools.

Learn more about Aurora

Corporate Headquarters: 2220 Lundy Drive, San Jose, CA 95131 USA 1-408-990-4000 | info@quicklogic.com:

Sales Offices: https://www.quicklogic.com/company/sales-locations/

North America: america-sales@quicklogic.com | China: asia-sales@quicklogic.com | Japan: japan-sales@quicklogic.com

Korea: korea-sales@quicklogic.com | Taiwan: asia-sales@quicklogic.com | United Kingdom: europe-sales@quicklogic.com