Buy Now

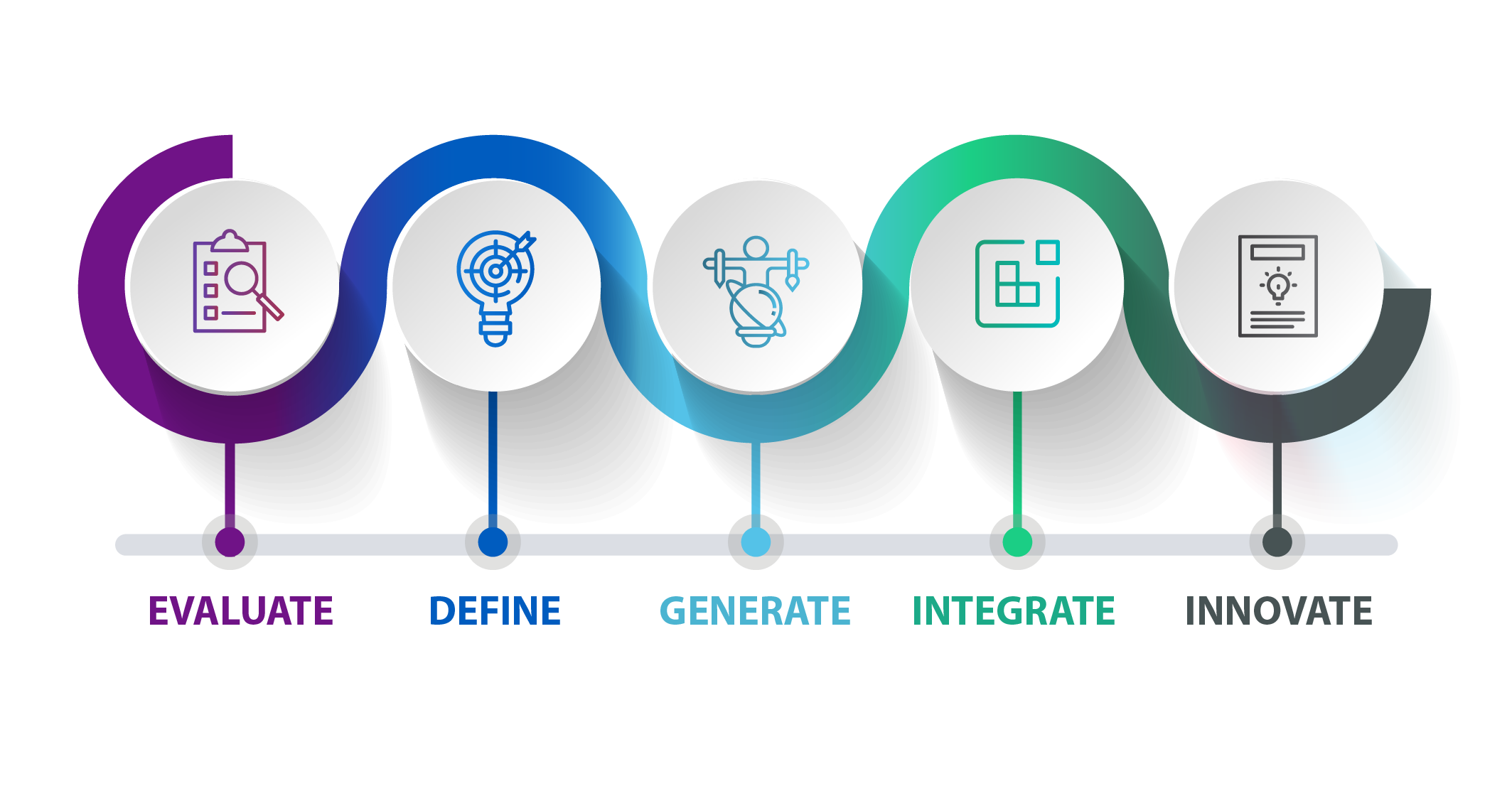

ステップ 1: 必要な eFPGA IP の要件を把握

ヘテロジニアスな eFPGA (LUT、DSP ブロック、ブロック RAM など) のパーティショニング

クイックロジックの継続的なベンチマーク システムを活用し、標準的なベンチマーク デザインまたは独自のデザインを使用して eFPGA の最適なアーキテクチャとサイズを決定

ステップ 2: 要件を満たす eFPGA IP を定義

ステップ 1 の評価結果に基づいて、クイックロジックの Australis ツールを使用して性能要件とエリア要件を満たすように eFPGA のロジックアレイを最適化

ロジックの種類、RAM、DSP などのリソースを定義する。またカスタム eFPGA IP を構築するにあたってこれらの組み合わせを定義

SoC/ASIC のフロアプランに合わせて eFPGA のアレイ サイズとアスペクト比を定義

統合のため、eFPGA から ASIC へのポート マッピングを作成

ステップ 3: Australis ツールで IP ファイルを生成

ステップ 1 の評価結果に基づいて、クイックロジックの Australis ツールを使用して性能要件とエリア要件を満たすように eFPGA のロジックアレイを最適化

ロジックの種類、RAM、DSP などのリソースを定義する。またカスタム eFPGA IP を構築するにあたってこれらの組み合わせを定義

SoC/ASIC のフロアプランに合わせて eFPGA のアレイ サイズとアスペクト比を定義

統合のため、eFPGA から ASIC へのポート マッピングを作成

ステップ 4: 生成した eFPGA を SoC に統合

設計における目標を達成する - 性能、コスト、市場投入までの期間など

クイックロジックの経験豊富な FPGA 設計チームがテスト ベクターの生成など、eFPGA IP を独自のチップに統合するまでの包括的な開発フローをサポートし、プロジェクトのリスクを軽減

ステップ 5: イノベーションを追求

eFPGA を搭載したデバイスが製品化された後もクイックロジックのサポートは継続

完全オープンソースの SymbiFlow やクイックロジックの Aurora FPGA 設計環境のアドバンス機能を使用して、独自の eFPGA デザインを管理

ランタイムの短縮 & タイミング解析機能が統合

進化するツールを活用することで、開発者はイノベーションに集中し、製品価値を向上させることが可能

We use cookies to ensure that we give you the best experience on our website. If you continue to use this site we will assume that you are happy with it. Ok